美国SiTime晶振,3225贴片晶振,SiT9120系列,差分晶振,进口陶瓷晶振,服务器晶振

美国SiTime晶振,3225贴片晶振,SiT9120系列,差分晶振,进口陶瓷晶振,服务器晶振

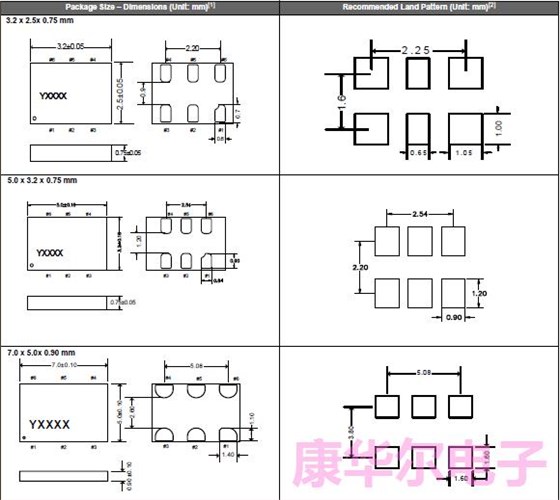

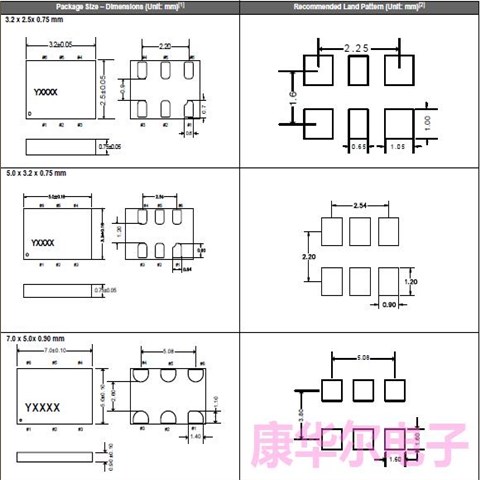

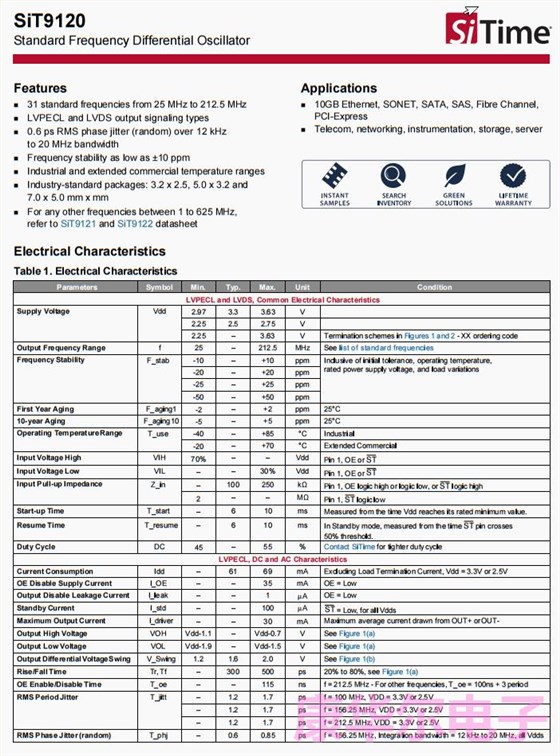

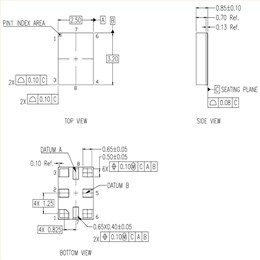

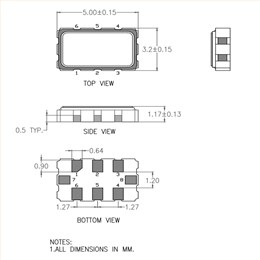

美国SiTime硅晶振中的SiT9120系列为差分晶振,频率范围是25~212.5MHz,进口陶瓷晶振,有源晶振,六脚贴片晶振,LVPECL和LVDS输出,0.6 ps RMS相位超过12 kHz到20 MHz带宽的抖动(随机),频率稳定性低至±10 ppm,工业和扩展的商业温度范围,行业标准包装:3.2 x 2.5、5.0 x 3.2和7.0 x 5.0 mm x mm。产品很适用于10GB以太网、SONET、SATA、SAS、光纤通道、PCI-Express,电信,网络,仪器仪表,存储,服务器等。差分晶振可提供两种相位彼此完全相反的信号, 差分晶体振荡器属于行业里极其高端的有源晶振,拥有 LVDS,LVPECL,HCMOS 等输出方式,我们常见的是贴片差分晶振,体积有微小型也有大体积,常规的输出方式是 LVDS,因此在业界中还有 LVDS 差分晶振这一说法,军事设备与工业设备应用比较比较多。

差分晶振是一种常见的电子元件,可用于许多应用领域。

1. 提高抗干扰能力:差分晶振通过在输入和输出引脚之间使用差分信号传输,可以主动抵消电磁干扰和噪声干扰,提高系统的抗干扰能力。

2. 减小时钟抖动:差分晶振可以减小时钟信号的抖动程度,提供更稳定、更精确的时钟信号,有助于提高系统的性能和稳定性。

3. 改善时钟信号传输质量:差分晶振可以在时钟信号传输过程中提供更高的信号品质,能够有效降低信号传输的损耗和失真,提高信号传输的可靠性和稳定性。

4. 增加噪声容限:差分晶振可以增加时钟信号的噪声容限,提供更大的时钟信号幅度,降低时钟信号的失真和抖动,有助于保持信号的完整性和准确性。

美国SiTime晶振,3225贴片晶振,SiT9120系列,差分晶振,进口陶瓷晶振,服务器晶振

美国SiTime晶振,3225贴片晶振,SiT9120系列,差分晶振,进口陶瓷晶振,服务器晶振

| Parameters | Symbol | Min. | Typ. | Max. | Unit | Condition | |||||||||||||||||

| LVPECL and LVDS, Common Electrical Characteristics | |||||||||||||||||||||||

| Supply Voltage | Vdd | 2.97 | 3.3 | 3.63 | V | ||||||||||||||||||

| 2.25 | 2.5 | 2.75 | V | ||||||||||||||||||||

| 2.25 | – | 3.63 | V | Termination schemes inFigures 1 and 2- XX ordering code | |||||||||||||||||||

| Output Frequency Range | f | 25 | – | 212.5 | MHz | Seelist of standard frequencies | |||||||||||||||||

| Frequency Stability | F_stab | -10 | – | +10 | ppm |

Inclusive of initial tolerance, operating temperature,

rated power supply voltage, and load variations

|

|||||||||||||||||

| -20 | – | +20 | ppm | ||||||||||||||||||||

| -25 | – | +25 | ppm | ||||||||||||||||||||

| -50 | – | +50 | ppm | ||||||||||||||||||||

| First Year Aging | F_aging1 | -2 | – | +2 | ppm | 25°C | |||||||||||||||||

| 10-year Aging | F_aging10 | -5 | – | +5 | ppm | 25°C | |||||||||||||||||

| Operating Temperature Range | T_use | -40 | – | +85 | °C | Industrial | |||||||||||||||||

| -20 | – | +70 | °C | Extended Commercial | |||||||||||||||||||

| Input Voltage High | VIH | 70% | – | – | Vdd |

Pin 1, OE or ST

|

|||||||||||||||||

| Input Voltage Low | VIL | – | – | 30% | Vdd |

Pin 1, OE or ST

|

|||||||||||||||||

|

Input Pull-up Impedance

|

Z_in |

– | 100 | 250 | kΩ |

Pin 1, OE logic high or logic low, or ST logic high

|

|||||||||||||||||

| 2 | – | – | MΩ |

Pin 1, ST logic low

|

|||||||||||||||||||

| Start-up Time | T_start | – | 6 | 10 | ms | Measured from the time Vdd reaches its rated minimum value. | |||||||||||||||||

|

Resume Time |

T_resume |

– |

6 |

10 |

ms |

In Standby mode, measured from the time ST pin crosses

50% threshold. |

|||||||||||||||||

| Duty Cycle | DC | 45 | – | 55 | % | Contact SiTimefor tighter dutycycle | |||||||||||||||||

美国SiTime晶振,3225贴片晶振,SiT9120系列,差分晶振,进口陶瓷晶振,服务器晶振

美国SiTime晶振,3225贴片晶振,SiT9120系列,差分晶振,进口陶瓷晶振,服务器晶振

更多相关美国Sitime晶振型号,请咨询我们!

EPSON低耗能振荡器,X1M000341002200,XG-2102CA光模块晶振

EPSON低耗能振荡器,X1M000341002200,XG-2102CA光模块晶振 SG-770SDD路由器晶振,X1G002361000700,爱普生LV-PECL低抖动晶振

SG-770SDD路由器晶振,X1G002361000700,爱普生LV-PECL低抖动晶振 瑞萨GPS定位晶振,XTL312156.250000I,交换机差分晶振

瑞萨GPS定位晶振,XTL312156.250000I,交换机差分晶振 瑞萨LVDS差分石英晶振,XPL536156.250000I,物联网应用晶振

瑞萨LVDS差分石英晶振,XPL536156.250000I,物联网应用晶振 XUO730200.000000X,Renesas物联网晶振,蓝牙模块晶振

XUO730200.000000X,Renesas物联网晶振,蓝牙模块晶振 QC1624.0000F18B42R,Qantek家电影音晶振,QC16四脚石英晶体

QC1624.0000F18B42R,Qantek家电影音晶振,QC16四脚石英晶体 151系列,151-13.000M-SR-05HS-VS,美国Oscilent插件晶体,13MHZ

151系列,151-13.000M-SR-05HS-VS,美国Oscilent插件晶体,13MHZ SiT1630AI-H4-DCC-32.768S,2012贴片晶振,32.768K振荡器,美国SiTime晶振

SiT1630AI-H4-DCC-32.768S,2012贴片晶振,32.768K振荡器,美国SiTime晶振